El enunciado del ejercicio es el siguiente: Implementar en el CPLD XC9572 un Contador BCD con permiso de reloj y borrado asíncrono. Su salida será decodificada a 7 segmentos sobre una DISPLAY de cátodo común de 7 segmentos.

Creamos un nuevo proyecto al igual que en los anteriores ejercicios. Colocamos un contador BCD, al que ya hemos añadido el BUFG para minimizar el skew

Tenemos que diseñar el decodificador, en este caso, en código VHDL. Seguimos los siguientes pasos:

Continuamos y se nos crea un fichero .vhd, si nos adentramos en él veremos un código como este

Tenemos las librerias creadas y la cabecera pero nos falta el programa en si, que lo podemos conseguir de las plantillas VHDL que el mismo programa nos proporciona. Para ello vamos a Edit-> Language Templates y buscamos un display de 7 segmentos, copiamos el código que nos haga falta en nuestro programa y ya estará

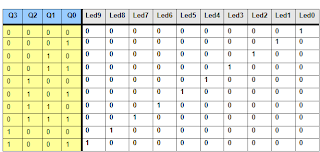

Teniendo en cuenta que dependiendo si el display es de ánodo común o de cátodo común habrá que cambiar los ceros por unos y viceversa (en la imagen es ánodo común) así que nosotros lo vamos a cambiar.

Ahora vamos a crear el símbolo y conectamos todo

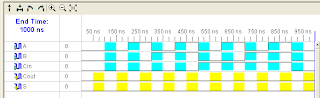

Creamos el Test Bench como ya hemos hecho en otros ejercicios y nos vamos al ModelSim

Asignamos los pines como en la imagen

Y finalmente programar en la tarjeta, como ya hemos visto.