We will use ISE Webpack 10.1, that is a Xilinx´s application and a CPLD XC9572.

Other aplication that we have to use is ModelSim that is another application whose function is to simulate the exercise.

Our first exercise is: IMPLEMENT A 1 BIT ADDER using a CPLD (XC9572, in my case).

To understand the operation of our adder, we have to make a true table:

This table contains two input data (A and B) + the input Carry and a output data + the output Carry.

If we apply Karnaugh, our result is as follows:

The next step is to design a schematic circuit. For this, we have to open ISE Webpack 10.1 (Project Navigator) and we must select 'File'--> 'New Project'.

Now, will be opened a window like this:

Here, we must put the Project name (sumador) and the Project location (C:\Xilinx\Projects\sumador). At last we need to select the type of source for the project that will be 'Schematic'.

In the next window, we have must to configure our device properties. The device and the family are XC9572 and XC9500 CPLDs respectively. Our Package is PC84 and the speed -7.

Later we must select the programming language that we prefer, I prefer VHDL.

To simulate the program, I have to use ModelSim simualator.

In the new window, we select Schematic for the design and we put the Location and the File name.

In the next window we click next because we don´t need to add any source.

Now will be opened a new window with the working environment.

We have to go to 'Symbols' tab for select our components. In the window´s top there is a toolbar where we can select different options like 'Add wire' or 'Add Net name'.

We begin to select the components (2 AND gates, 2 XOR, 1 OR gate) and we add the nets.

Create the Test Bench file, for this, we need to create a new source and we select Test Bench Waveform.

In this window we should select the internal clock like in the image:

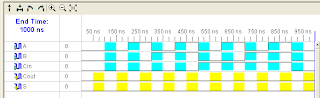

Now, we have to check the true table of the counter. We need to configure the time inputs for realize the simulation.

We have to add the Test Bench file to project and it will be opened ModelSim with the simulation.

Finally, we have to program the project in a CPLD.

For this we need a JTAG

An ATX power source

and the CPLD 'TAD-XC9572'.

At first we have to generate our programming file (.JED file)

When we had generated the .JED, we must go to Impact (Xilinx´s application). And program the CPLD.

0 comentarios:

Publicar un comentario