Utlizando el Orcad Capture, hemos propuesto crear un entrenador con el PIC18F4550. Para poder realizar este proyecto deberemos estudiar el datasheet del pic, que podemos ver aquí.

Como he dicho, vamos a utilizar el Orcad Capture y mas adelante utilizaremos el Layout, que son unas aplicaciones de Cadence para el diseño y desarrollo de circuitos electrónicos.

Abrimos Orcad Capture y podemos empezar

Lo primero que debemos hacer es crear la librería del PIC en el Capture, ya que no viene por defecto. Lo que podemos hacer es coger como plantilla cualquier otro pic que ya exista y guiándonos por el datasheet del PIC18F4550, ir modificando cada patilla de nuestra plantilla hasta que sea idéntico al esquema real del pic. Sino es así, a la hora de llevarlo a la realidad nunca funcionará correctamente.

Una vez terminada nuestra plantilla, y todos nuestros pines esten igual que en el datasheet del 18F4550 ya se podrá utilizar en la librería parar realizar el proyecto, vamos avanzando y haciendo las conexiones pertinentes, en este caso con los buses que determinarán los distintos puertos. Así como también deberemos ir colocándo etiquetas a cada pista y pin que utilicemos.

Una vez esté todo etiquetado, es decir, las conexiones hechas empezaremos a diseñar los distintos bloques que contendrá nuestro proyecto.

Lo primero que vamos a hacer va a ser el RESET y el OSCILADOR EXTERNO. El reset símplemente será un pulsador para poder realizar un reset manual al PIC cuando lo necesitemos. El oscilador externo contiene un cristal de 20MHz, que es para determinar la frecuancia a la que trabajará el pic (su reloj).

Ahora vamos a poner un CONECTOR RIBBON que es un bloque de ampliación por si quisieramos conectar algún periferico externo mas adelante.

El siguiente bloque consistirá en las interrupciones. Habrá dos, una externa y la RB4 con un pulsador cada una para ponerlas a cero.

El siguiente bloque contiene un conector DB9, el cual permitirá la conexión del PIC con el PC mediante una conexión RS-232.

Ahora introduciremos un Display LCD gráfico y otro Display común de 7 segmentos para coformar el bloque de la visualización.

Otro de los bloques que hay es un ICD2 para poder realizar una comunicación en lenguaje Assembler o C con el Mplab. Así podremos programar los distintos integrados que dispondrá nuestra placa.Una vez finalizados todos los bloques hay que unirlos y conexionarlos entre sí, ya que hasta ahora cada bloque que hemos hecho lo hemos realizado por separado.

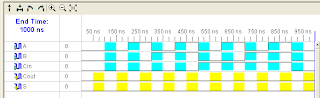

Cuando hayamos realizado todas las conexiones entre los bloques que contendrá la placa nos queda por comprobar los posibles errores que existan. Para ello nos vamos a DRC para que nos muestre el log con todos los errores y warnings existentes

Como veis en la imagen tengo bastantes warning pero no hace falta eliminarlos todos, solo los que nos impidan poder llevar la placa a la realidad.

Aquí terminaría nuestro proyecto en Orcad Capture.

Para seguir el proceso en Layout: AQUÍ